|

EJERCICIOS COMBINACIONALES |

EJERCICIO 1 (Examen del Plan Antiguo Electrónica II Junio 2000/1 2ª Prueba Personal 1 ª Semana, Junio 2002/03 2º Semana , Septiembre 2002/03 Reserva, Septiembre 2004/05 y Septiembre 2005/06)

Realice un circuito combinacional minimizado con puertas lógicas que implemente un circuito que realice el complemento a dos de un número de cuatro bits.

EJERCICIO 2 (Examen del Plan Antiguo Electrónica II Junio 2000/1 2ª Prueba Personal 2 ª Semana)

Minimice e implemente con decodificadores de cuatro entradas un circuito detector de pariedad impar (número de unos impar) de un número digital de 5 entradas.

EJERCICIO 3 (Examen del Plan Antiguo Electrónica II Junio 2001/2 2ª Prueba Personal 1 ª Semana)

Diseñe y minimice un sistema combinacional capaz de realizar la multiplicación de dos números binarios, de un dígito cada uno. El sistema tendrá una señal de acarreo de entrada, y una señal de acarreo de salida. Describa el método de generalización del problema para números de un número mayor de dígitos binarios.

EJERCICIO 4 (Examen del Plan Antiguo Electrónica II Junio 2001/2 2ª Prueba Personal 2 ª Semana y Junio 2002/03 1º Semana)

Implemente un circuito de 5 variables de entradas con decodificadores de 4 entradas

S=f(A,B,C,D,E) =m1+m2+m15+m16+m17+m28+m29+m30+m31

EJERCICIO 5 (Examen del Plan Antiguo Electrónica II Junio 2003/4 2ª Prueba Personal 1ª Semana)

Para el control de un proceso se precisa un sistema que actúe de la siguiente manera: al producirse un fallo en el proceso a controlar (E=0, no hay error; E=1, si hay error), el circuito de control lee el estado de dos variables lógicas E1 y E2, y en función de la combinación lógica que presenten actúa uno de los cuatro posibles sistemas de control existentes, actuándose sobre su señal de entrada, S1, S2, S3 y S4. Dibuje el diagrama de bloques del sistema e implemente un circuito que responda a estas características con el mínimo número de puertas.

EJERCICIO 6 (Examen del Plan Antiguo Electrónica II Junio 2003/4 2ª Prueba Personal 2 ª Semana)

Realice con multiplexores de cuatro canales y puertas la función lógica siguiente:

S= f(A,B,C,D)= m0+m4+m5+m6+m7+m9+m13+m15

EJERCICIO 7 (Examen del Plan Antiguo Electrónica II Junio 2004/5 2ª Prueba Personal 1ª Semana)

Diseñe a partir del mapa de Karnaugh con puertas lógicas, un circuito multiplexador de cuatro entradas, así como otro demultiplexador de cuatro salidas. Dibuje el diagrama de bloques y el circuito con puertas lógicas.

EJERCICIO 8 (Examen del Plan Antiguo Electrónica II Junio 2004/5 2ª Prueba Personal 2 ª Semana)

Realice un circuito combinacional minimizado con puertas lógicas, que implemente un circuito que realice la resta de dos números de dos bits, codificados en complemento a dos, con salida en complemento a dos, igualmente.

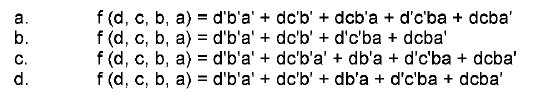

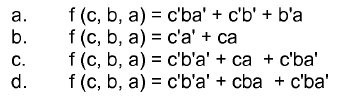

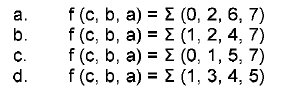

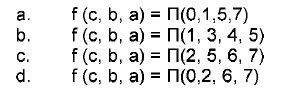

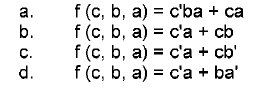

Utilizando decodificadores generar las funciones lógicas siguientes:

![]()

![]()

EJERCICIO 10 (Examen del Plan Antiguo Electrónica II Septiembre 2006/7 Reserva y Junio 2008/9 2 ª Semana)

Dada la expresión lógica, impleméntela mediante multiplexores de cuatro canales.

EJERCICIO 11 (Examen del Plan Nuevo Electrónica Digital Junio 2005/6 1 ª Semana)

Se tiene un sistema digital cuya función canónica es:

f = m0+m1+m2+m4+m8+m10

Indique la expresión más simplificada mediante Karnaugh:

a) CA+DBA+DCB

b) CBA+DCA+DCB

c) ![]()

d) ![]()

Exprese la función en sumas canónicas o Maxterms:

a) f = M3M5M6M7M9M11M12M13M14M15

b) f = M0M1M2M4M8M10

c) f = M12M10M9M8M6M4M3M2M1M0

d) f = M15M14M13M11M7M5

EJERCICIO 12 (Examen del Plan Nuevo Electrónica Digital Septiembre 2005/6 )

Realice las siguientes conversiones de funciones lógicas digitales:

Exprese la siguiente función como sumas canónicas o Maxterms.

![]()

a) f = M0M1M2M3M5M6M8M9M10M11M14

b) f = M1M2M3M4M5M6M8M9M10M11M14

c) f = M1M2M3M4M5M6M7M8M10M12M14

d) f = M0M1M2M4M5M6M7M8M10M12M14

Exprese como sumas de minterms:

f = M1M2M3M4M5M6M7M8M10M12M14

a) f = m1+m2+m4+m12+m15

b) f = m1+m2+m4+m12+m15

c) f = m0+m2+m4+m6+m15

d) f = m0+m2+m4+m12+m15

¿Qué término podría añadirse a la función lógica f = m0+m2+m3+m8+m11 para optimizar la simplificación por el mapa de Karnaugh?

a) m10

b) m14

c) m15

d) m9

EJERCICIO 13 (Examen del Plan Nuevo Electrónica Digital Junio 2006/7 1ª Semana)

Dada la siguiente expresión booleana

![]()

Exprese su función canónica en suma de minterms:

a) f = m0+m1+m3+m4+m6+m8+m9+m12+m13

b) f = m2+m5+m7+m10+m14+m15

c) f = m1+m3+m4+m6+m8+m9+m10+m12+m14+m15

d) f = m1+m2+m3+m4+m5+m8+m9+m11+m13

Indique la expresión más simplificada mediante Karnaugh:

a) ![]()

b)![]()

c)![]()

d)![]()

EJERCICIO 14 (Examen del Plan Nuevo Electrónica Digital Junio 2005/6 2 ª Semana)

Se tiene un sistema digital cuya función canónica es:

f = m0+m2+m7+m8+m15

Indique la expresión más simplificada mediante Karnaugh:

a) ![]()

b) ![]()

c) ![]()

d) ![]()

¿Qué término se podría añadir como indiferente para minimizar considerablemente la expresión de la función?

a) m14

b) m11

c) m13

d) m10

EJERCICIO 15 (Examen del Plan Nuevo Electrónica Digital Junio 2006/7 2 ª Semana)

Dada la siguiente expresión booleana.

![]()

Simplifique la expresión mediante el método de Karnaugh

a) ![]()

b) ![]()

c) ![]()

d) ![]()

Exprese su función canónica en producto de sumas canónicas o maxterms

a) M0M1M3M4M8M9M12M13

b) M2M5M6M7M8M11M12M14M15

c) M1M2M7M8

d) M0M1M2M4M8M9M10M13

EJERCICIO 16 (Examen del Plan Nuevo Electrónica Digital Junio 2005/6 2 ª Semana)

A partir del siguiente circuito lógico:

Exprese el valor de su función lógica reducida f(d,c,b,a).

a) f(d,c,b,a)=(a´+b´)(a´+c´)(b´+c´+d´)

b) f(d,c,b,a)=(a+b)´(a+c)´(b+c+d)´

c) f(d,c,b,a)=((a+b)´(a+c)´(b+c+d)´)´

d) f(d,c,b,a)=(a+b)(a+c)(b+c+d)

Reduzca la siguiente función de Maxterms por ceros de Karnaugh: f = M3M5M7M11M13M14M15 e indique el resultado obtenido:

a) f(d,c,b,a)=((a+b)´(a+c)´(b+c+d)´)´

b) f(d,c,b,a)=(a+b)(a+c)(b+c+d)

c) f(d,c,b,a)=(a´+b´)(a´+c´)(b´+c´+d´)

d) f(d,c,b,a)=(a+b)´(a+c)´(b+c+d)´

Exprese la función canónica en productos canónicos o mínterms.

a) m15 +m14+ m13+ m11+ m9+ m7+ m6+ m5+ m3

b) m15 +m14+ m13+ m11+ m7+ m5+ m3

c) m12 +m10+ m8+ m4+ m2+ m1+ m0

d) m12 +m11+ m9+ m8+ m6+ m3+ m2+ m1+ m0

EJERCICIO 17 (Examen del Plan Nuevo Electrónica Digital septiembre 2005/6 Reserva)

Se tiene un sistema digital cuya función canónica es:

f(D,C,B,A) = m0+m1+m4+m5+m8+m9+m10

Indique la expresión más simplificada mediante Karnaugh:

a) f = DB+CB+D´CA.

b) f = D´B´+C´B´+DC´A´

c) f = D´C´B´+C´B´A+DCB

d) f = DCB+CBA´+D´C´B´.

¿Qué término se podría incluir como indiferente para optimizar la función obtenida?

a) m2

b) m3

c) m6

d) m14

EJERCICIO 18 (Examen del Plan Nuevo Electrónica Digital septiembre 2006/7 Reserva)

Dada la siguiente función lógica de tres variables, indicar la función canónica equivalente:

![]()

a) m2+m3

b) m4+m5

c) M2M3

d) m0+m1+m2+m3+m6+m7

EJERCICIO 19 (Examen del Plan Nuevo Electrónica Digital septiembre 2006/7 Reserva)

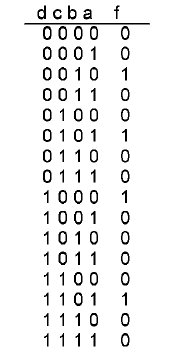

Dada la siguiente tabla de verdad, encuentre la expresión simplificada por unos mediante Karnaugh.

| d | c | b | a | f |

|---|---|---|---|---|

0 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

1 |

0 |

1 |

0 |

0 |

1 |

1 |

0 |

0 |

1 |

0 |

0 |

1 |

0 |

1 |

0 |

1 |

0 |

0 |

1 |

1 |

0 |

1 |

0 |

1 |

1 |

1 |

0 |

1 |

0 |

0 |

0 |

1 |

1 |

0 |

0 |

1 |

0 |

1 |

0 |

1 |

0 |

X |

1 |

0 |

1 |

1 |

X |

1 |

1 |

0 |

0 |

X |

1 |

1 |

0 |

1 |

X |

1 |

1 |

1 |

0 |

X |

1 |

1 |

1 |

1 |

X |

a) a´

b) a

c) b+b´

d) dc+a´

Realizar un multiplexor de 16 canales basado en multiplexores de 8 canales.

Realizar un multiplexor de 32 canales basado en multiplexores de 8 canales.

Se disponen de dos fuentes de datos en paralelo de 4 bits cada uno. Realizar un circuito con el cual se pueda seleccionar, mediante una variable, cuál de los dos datos pasa a un bus de datos general.

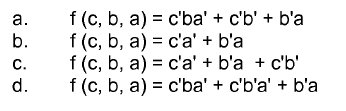

Realizar mediante multiplexores las funciones lógicas siguientes:

f1 = m0+m2+m3+m5+m6

![]()

Diseñar un sistema decodificador de cuatro variables de entrada (24=16 salidas) a partir de decodificadores de tres variables de entrada (23=8 salidas).

Diseñar un sistema decodificador de seis variables de entrada ( 26=64 salidas) a partir de decodificadores de cuatro variables de entrada (24=16 salidas).

Diseñar un comparador de datos de 1 bit, de manera que se pueda detectar si son iguales o uno mayor o menor que el otro. Describir el método de generalización del problema para datos de un número mayor de dígitos binarios (bits).

Diseñar un bloque decodificador de cinco variables (32 salidas) basándose en el decodificador 4:16 y los circuitos auxiliares que sean necesarios.

Deducir la expresión algebraica en minterms de los siguientes circuitos:

a)

b)

Diseñar mediante el circuito integrado 74153 un circuito que realice simultáneamente las funciones:

f1 = m1+m2+m4

![]()

EJERCICIO 30 (Examen del Plan Antiguo Electrónica II Junio 2007/8 1 ª Semana)

Implementar un circuito con 5 variables de entrada con decodificadores de 4 entradas que realice la siguiente función:

S = f(A, B, C, D, E) = m1+m2+m3+m7+m12+m31

EJERCICIO 31 (Examen del Plan Antiguo Electrónica II Junio 2008/9 1 ª Semana)

Implementar un circuito con 5 variables de entrada con multiplexadores de 8 entradas que realice la siguiente función:

S = f(A, B, C, D, E) = m1+m2+m3+m6+m9+m11+m19+m21

EJERCICIO 32 (Examen del Plan Nuevo Electrónica Digital Junio 2007/8 1 ª Semana)

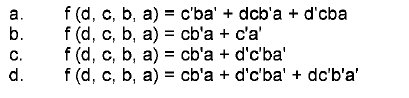

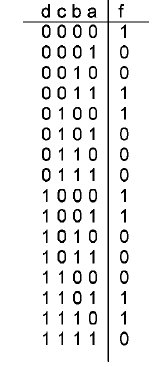

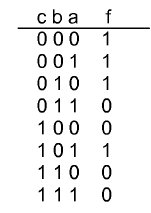

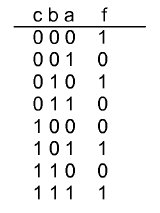

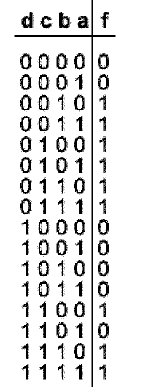

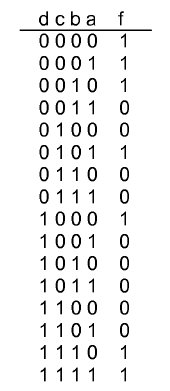

Dada la siguiente Tabla de Verdad:

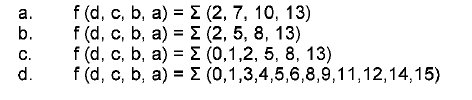

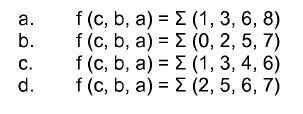

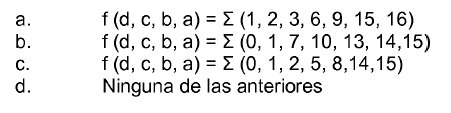

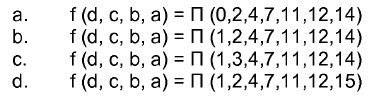

Determine cuál es su función canónica en minitérminos (minterms):

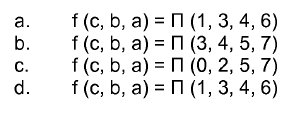

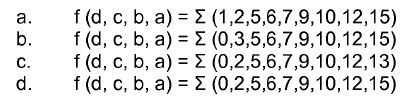

Determine cuál es su función canónica en maxitérminos (maxterms):

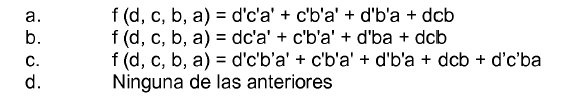

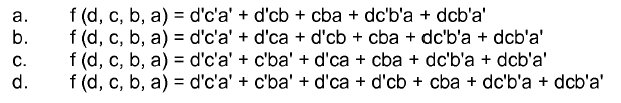

Simplifique la expresión por el método de Karnaugh:

EJERCICIO 33 (Examen del Plan Nuevo Electrónica Digital Junio 2007/8 2 ª Semana)

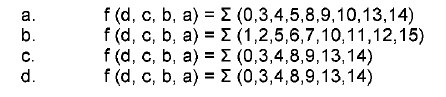

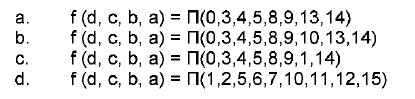

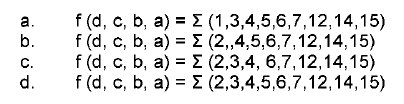

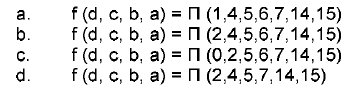

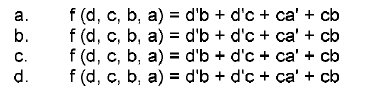

Dada la siguiente Tabla de Verdad:

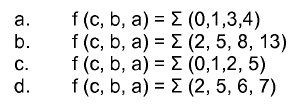

Determine cuál es su función canónica en minitérminos (minterms):

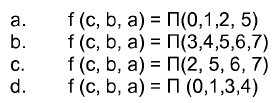

Determine cuál es su función canónica en maxitérminos (maxterms):

Simplifique la expresión por el método de Karnaugh:

EJERCICIO 34 (Examen del Plan Nuevo Electrónica Digital Junio 2008/9 1 ª Semana)

Dada la siguiente Tabla de Verdad:

Determine cuál es su función canónica en minitérminos (minterms):

Determine cuál es su función canónica en maxitérminos (maxterms):

Simplifique la expresión por el método de Karnaugh:

EJERCICIO 35 (Examen del Plan Nuevo Electrónica Digital Junio 2008/9 2 ª Semana)

Dada la siguiente Tabla de Verdad:

Determine cuál es su función canónica en minitérminos (minterms):

Determine cuál es su función canónica en maxitérminos (maxterms):

Simplifique la expresión por el método de Karnaugh:

EJERCICIO 36 (Examen del Plan Nuevo Electrónica Digital septiembre 2007/8)

Dada la siguiente Tabla de Verdad:

Determine cuál es su función canónica en minitérminos (minterms):

Determine cuál es su función canónica en maxitérminos (maxterms):

Simplifique la expresión por el método de Karnaugh:

EJERCICIO 37 (Examen del Plan Nuevo Electrónica Digital septiembre 2007/8 reserva)

Dada la siguiente Tabla de Verdad:

Determine cuál es su función canónica en minitérminos (minterms):

Determine cuál es su función canónica en maxitérminos (maxterms):

Simplifique la expresión por el método de Karnaugh:

EJERCICIO 38 (Examen del Plan Nuevo Electrónica Digital septiembre 2008/9)

Dada la siguiente Tabla de Verdad:

Determine cuál es su función canónica en minitérminos (minterms):

Simplifique la expresión por el método de Karnaugh:

EJERCICIO 39 (Examen del Plan Nuevo Electrónica Digital septiembre 2008/9 reserva)

Dada la siguiente Tabla de Verdad:

Determine cuál es su función canónica en minitérminos (minterms):

Determine cuál es su función canónica en maxitérminos (maxterms):

Simplifique la expresión por el método de Karnaugh:

EJERCICIO 40 (Examen del Plan Nuevo Electrónica Digital Junio 2007/8 2 ª Semana)

Se dispone de multiplexores de 4:1 con dos entradas de selección y una de inhibición, se pide:

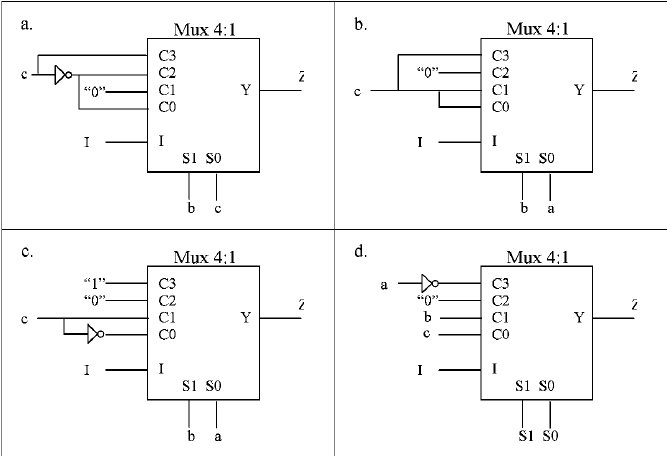

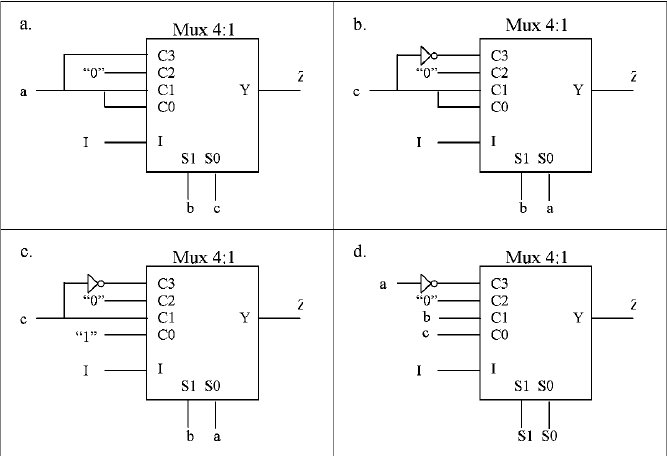

a) Determinar cuál de los siguientes circuitos cumple la función lógica Z = cb´a´ + cb´a + c´ba:

b) Si se desea implementar un circuito selector de datos de 4 bits a partir del multiplexor anterior, determine qué acciones se deberán llevar a cabo:

1 Utilizar 4 Mux 4:1 colocados en paralelo compartiendo los bits de selección, y otro más que reciba como entradas las salidas de los anteriores.

2 Utilizar 4 Mux 4:1 colocados en paralelo compartiendo los bits de selección.

3 Aumentar el número de sus salidas utilizando para ello 8 Mux 4:1.

4 Ninguna de las anteriores.

EJERCICIO 41 (Examen del Plan Nuevo Electrónica Digital Junio 2008/9 2 ª Semana)

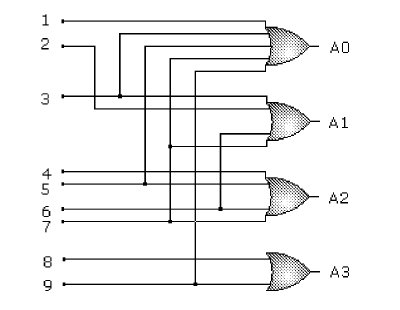

Basándonos en el siguiente circuito:

1) Si la entrada es 000000100, calcule la combinación en la salida:

a) 1111.

b) 0111.

c) 0011.

d) 0001,

2) Indique a qué tipo de circuito corresponde:

a) Multiplexor.

b) Codificador BCD a decimal.

c) Selector de datos.

d) Ninguna de las anteriores.

EJERCICIO 42 (Examen del Plan Nuevo Electrónica Digital septiembre 2007/8)

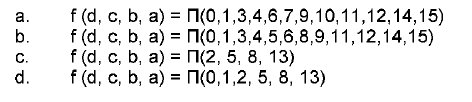

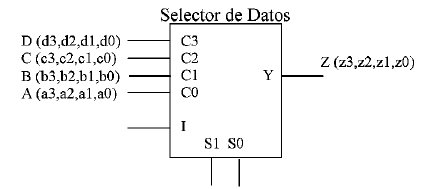

Mediante un multiplexor se pide realizar la siguiente función

Z = c´ba + c´b´a´ + cba´ + cba

Se pide, determinar cuál de estos circuitos es correcto: