EJERCICIO 7 (Examen del Plan Antiguo Electrónica II Junio 2004/5 2ª Prueba Personal 1ª Semana)

Diseñe a partir del mapa de Karnaugh con puertas lógicas, un circuito multiplexador de cuatro entradas, así como otro demultiplexador de cuatro salidas. Dibuje el diagrama de bloques y el circuito con puertas lógicas.

SOLUCIÓN:

Los MULTIPLEXORES son circuitos combinacionales que tienen varias entradas, una sola salida y varias líneas de selección. Su funcionamiento podría asemejarse a un conmutador de varias posiciones que simularían las entradas y el terminal común, la salida; la conmutación se realizaría por medio de la línea de selección, de tal modo que las señales presentes en las entradas aparecerán en la salida en el orden indicado por la línea de selección; es decir, un multiplexor permite el envío por una sola línea de los datos presentes en varias líneas.

Un multiplexor de cuatro entradas o canales dispone de: cuatro entradas (C0, C1, C2 y C3), dos entradas de selección (A y B) y una salida Y. El diagrama de bloques y la tabla de verdad son:

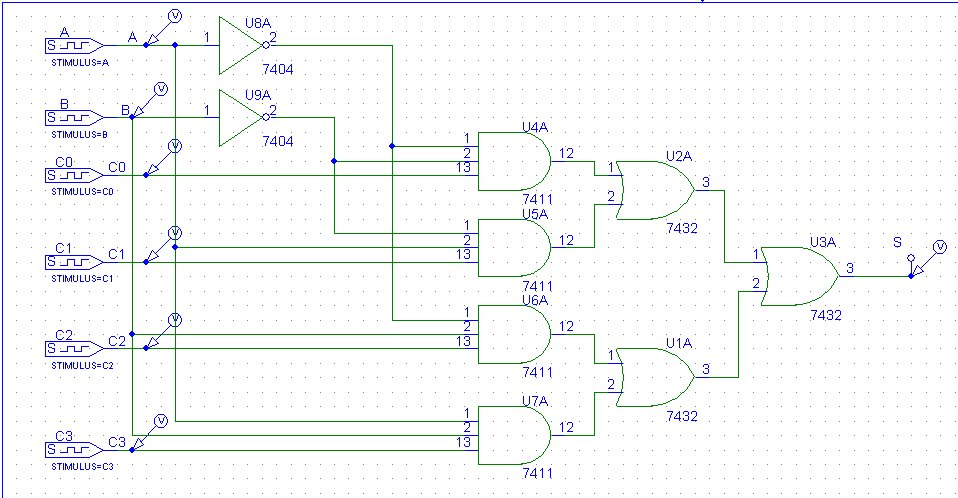

La expresión de la salida Y es: ![]() , cuyo circuito lógico es:

, cuyo circuito lógico es:

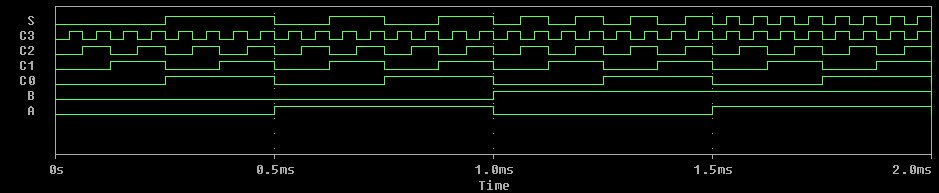

La simulación con DesignLab:

Los DEMULTIPLEXORES realizan la función inversa a la del multiplexor, es decir, una señal de entrada única, es obtenida en uno de los N canales de salida. El conmutador ahora selecciona el canal de salida por donde estará presente el dato de entrada.

El sistema tiene tres entradas:

E = dato

E1 y E2 = variables lógicas de selección

Las salidas del sistema son cuatro:

S1 = salida del canal 1.

S2 = salida del canal 2.

S3 = salida del canal 3.

S4 = salida del canal 4.

Por tanto, el dato E aparecerá en las señales de salida del sistema S1, S2, S3 o S4 según la combinación de entrada de las variables lógicas E1 y E2.

La tabla de verdad del sistema es:

Las funciones de las salidas deducidas de la tabla de verdad son:

No tienen posible simplificación al tener un sólo término cada una.

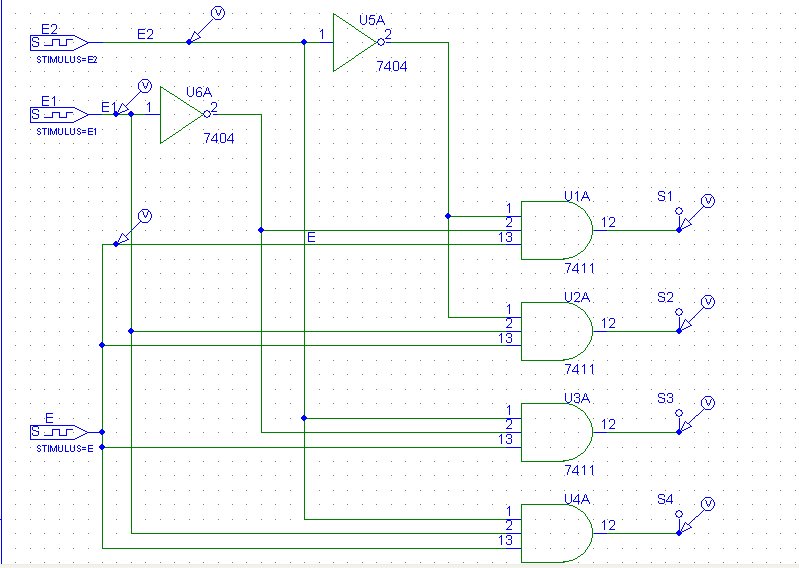

El circuito lógico con puertas lógicas es:

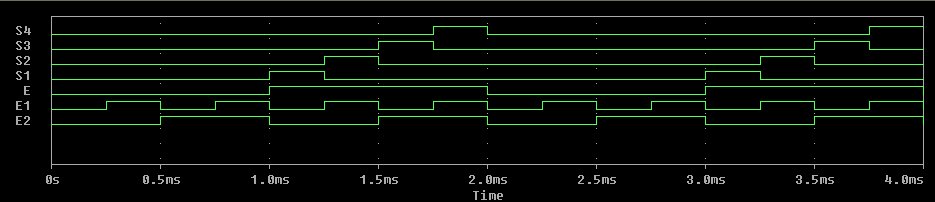

La simulación con DesignLab queda de la siguiente manera: