|

DEMULTIPLEXORES |

Los DEMULTIPLEXORES realizan la función inversa a la del multiplexor, es decir, una señal de entrada única, es obtenida en uno de los N canales de salida. El conmutador ahora selecciona el canal de salida por donde estará presente el dato de entrada.

Se denomina al demultiplexor por el número de canales de salida N. Así, por ejemplo, el demultiplexor 1:4 tiene 4 canales de salida.

DEMULTIPLEXOR 1:4 CON PUERTAS LÓGICAS:

Para poder seleccionar entre 4 canales de salidas necesitamos 2 entradas de selección. El sistema tiene tres entradas:

E = dato

E1 y E2 = variables lógicas de selección

Las salidas del sistema son cuatro:

S1 = salida del canal 1.

S2 = salida del canal 2.

S3 = salida del canal 3.

S4 = salida del canal 4.

Por tanto, el dato E aparecerá en las señales de salida del sistema S1, S2, S3 o S4 según la combinación de entrada de las variables lógicas E1 y E2.

La tabla de verdad del sistema es:

Las funciones de las salidas deducidas de la tabla de verdad son:

No tienen posible simplificación al tener un sólo término cada una.

El circuito lógico con puertas lógicas es:

Existen circuitos integrados demultiplexores disponibles comercialmente. Los más utilizados son:

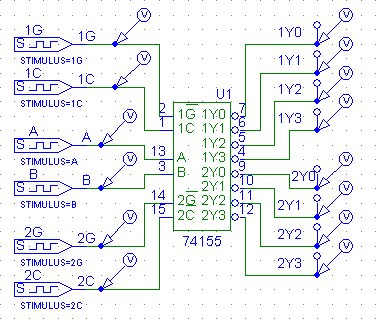

CIRCUITO INTEGRADO TTL 74155 DOBLE DECODIFICADOR 2:4/DEMULTIPLEXOR DE 1:4.

Este circuito integrado contiene dos demultiplexores 1:4, que también pueden funcionar como decodificadores 2 a 4.

La relación de pines de este integrado es la siguiente:

A y B: entradas de selección comunes a los dos demultiplexores activas a nivel alto (5V).

1G y 2G: entradas de inhibición o STROBE de los demultiplexores 1 y 2 respectivamente, activas a nivel bajo (0V).

1C y 2C: entradas del dato de los demultiplexores 1 y 2 respectivamente. 1C es activa a nivel alto (5V) y 2C es activa a nivel bajo (0V).

1Y0, 1Y1, 1Y2, 1Y3: salidas del demultiplexor 1 activas a nivel bajo (0V).

2Y0, 2Y1, 2Y2, 2Y3: salidas del demultiplexor 2 activas a nivel bajo (5V).

Con esta lógica en los pines, el dato 1C está invertido en las salidas 1Y0, 1Y1, 1Y2, 1Y3, mientras que el dato 2C no lo está en 2Y0, 2Y1, 2Y2, 2Y3.

La tabla de verdad y el montaje del demultiplexor 1 es la siguiente:

Podemos observar que cuando la entrada del Strobe (1G) está a 0 y la del dato (1C) está a 1, el demultiplexor 1 se comporta como un decodificador de dos entradas (A y B) y cuatro salidas activas a nivel bajo.

La tabla de verdad y el conexionado del demultiplexor 2 es la siguiente:

Podemos observar que cuando la entrada del Strobe (2G) y la del dato (2C) están a 0, el demultiplexor 2 se comporta como un decodificador de dos entradas (A y B) y cuatro salidas activas a nivel bajo.

Al estar la salida seleccionada a nivel bajo (0V) para visualizar la demultiplexación o la decodificación colocamos el LED de tal manera que se encienda cuando hay 0V a la salida y se apague con 5V en la salida.

El esquema de este componente en Microsim DesignLab es el siguiente:

La simulación de este circuito nos da el cronograma que puede compararse con su tabla de verdad pulsando las teclas a los lados de las tablas de verdad de cada uno de los dos multiplexores que contiene el circuito integrado 74155:

CIRCUITO INTEGRADO TTL 74138 DECODIFICADOR 3:8/DEMULTIPLEXOR DE 1:8.

Este circuito integrado contiene un demultiplexor 1:8, que también puede funcionar como decodificador 3 a 8.

La relación de pines de este integrado es la siguiente:

A , B y C: entradas de selección activas a nivel alto (5V).

E3 : entrada de validación o de dato activa a nivel alto (5V).

E2 y E1: entradas de validación activas a nivel bajo (0V).

Y0, Y1, Y2, Y3, Y4, Y5, Y6, Y7: salidas del demultiplexor activas a nivel bajo (0V).

La tabla de verdad y el montaje del demultiplexor es la siguiente:

Para que el circuito funcione como demultiplexor la entrada E3 tiene que estar a 1 y una de las otras dos (E2 ó E1) a 0. Si E2=0 el dato se introduce por E1 y si E1=0 el dato se introduce por E2. En ambos casos el dato es activo a nivel bajo al igual que las salidas.

Para realizar la decodificación las variables de validación deben valer E1=0, E2=0 y E3=1.

Al estar la salida seleccionada a nivel bajo (0V) para visualizar la demultiplexación o la decodificación colocamos el LED de tal manera que se encienda cuando hay 0V a la salida y se apague con 5V en la salida.

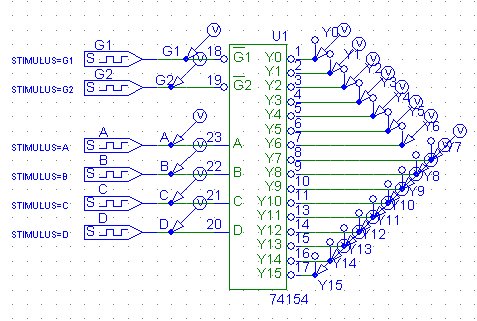

CIRCUITO INTEGRADO TTL 74154 DECODIFICADOR 4:16/DEMULTIPLEXOR DE 1:16.

Este circuito integrado contiene un demultiplexor 1:16, que también puede funcionar como decodificadores 4 a 16.

La relación de pines de este integrado es la siguiente:

A , B, C y D: entradas de selección activas a nivel alto (5V).

G1 y G2: entradas de validación o datos activas a nivel bajo (0V).

Y0, Y1, Y2, Y3, Y4, Y5, Y6, Y7, Y8, Y9, Y10, Y11, Y12, Y13, Y14, Y15: salidas del demultiplexor activas a nivel bajo (0V).

La tabla de verdad y el montaje del demultiplexor es la siguiente:

Al estar la salida seleccionada a nivel bajo (0V) para visualizar la demultiplexación o la decodificación colocamos el LED de tal manera que se encienda cuando hay 0V a la salida y se apague con 5V en la salida.

Podemos observar que cuando las entradas de validación G1 y G2 están a 0 (nivel bajo 0V), las entradas de selección marcan la salida activa a nivel bajo (0), funcionando como un decodificador 4 a 16.

Cuando G1=0, podemos introducir el dato por G2 (activo a nivel bajo 0V) y obtenerlo en la salida seleccionada por A, B, C y D también a nivel bajo (0V). Lo mismo ocurre si G2 = 0, ahora el dato podemos introducirlo por G1 (activo a nivel bajo 0V) y obtenerlo en la salida seleccionada por A, B, C y D también a nivel bajo (0V). Este funcionamiento sería como demultiplexor 1:16.

Cuando G1 = G2 = 1, todas las salidas están inactivas a nivel alto (5V), actuando G1 y G2 como entradas de inhibición del circuito integrado.

El esquema de este componente en Microsim DesignLab es el siguiente:

La simulación de este circuito nos da el cronograma que puede compararse con su tabla de verdad moviendo el rectángulo rojo de la tabla con MOVER TABLA o moviendo la línea roja del cronograma con MOVER CURSOR. Al pulsar el botón izquierdo del ratón el rectángulo y el cursor rojo se paran en la posición deseada. Para volver a moverlos pulsar MOVER TABLA o MOVER CURSOR.