EJERCICIO 40 (Examen del Plan Nuevo Electrónica Digital Junio 2007/8 2 ª Semana)

Se dispone de multiplexores de 4:1 con dos entradas de selección y una de inhibición, se pide:

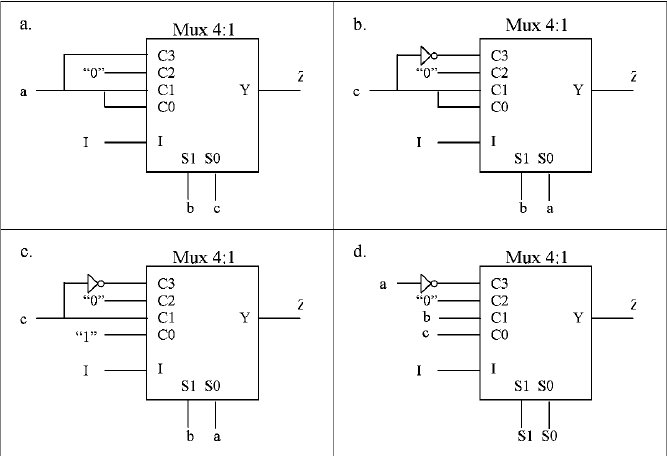

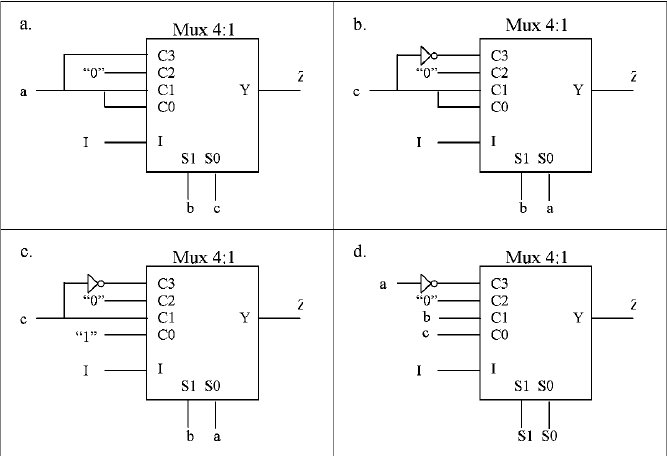

a) Determinar cuál de los siguientes circuitos cumple la función lógica Z = cb´a´ + cb´a + c´ba:

b) Si se desea implementar un circuito selector de datos de 4 bits a partir del multiplexor anterior, determine qué acciones se deberán llevar a cabo:

1 Utilizar 4 Mux 4:1 colocados en paralelo compartiendo los bits de selección, y otro más que reciba como entradas las salidas de los anteriores.

2 Utilizar 4 Mux 4:1 colocados en paralelo compartiendo los bits de selección.

3 Aumentar el número de sus salidas utilizando para ello 8 Mux 4:1.

4 Ninguna de las anteriores.

SOLUCIÓN:

Recordamos como funciona un multiplexor de cuatro canales: tiene dos entradas de selección S0 y S1, cuatro canales de entrada de datos C0, C1, C2 y C3 y una única salida Y. La combinación de las variables de selección S0 y S1 eligen el canal (C0, C1, C2 y C3) que comunicará su valor a la salida.

La entrada de inhibición I al tomar el valor "1" inhibe el funcionamiento del multiplexor.

Vamos a analizar cada uno de los circuitos:

a)

Comprobamos por la tabla de verdad el valor de Z:

Z = c´b´a + cb´a + cba

que no corresponde con la función lógica del enunciado.

b) Comprobamos por la tabla de verdad el valor de Z:

Z = c´ba + cb´a´ + cb´a

que corresponde con la función lógica del enunciado.

c) Comprobamos por la tabla de verdad el valor de Z:

Z = c´ba + cb´a´ + cb´a + c´b´a´

que no corresponde con la función lógica del enunciado.

d) En el circuito d la salida Z dependería de los valores de S0 y S1, no correspondiendo con la función lógica del enunciado.

Por tanto, la solución es el circuito b)

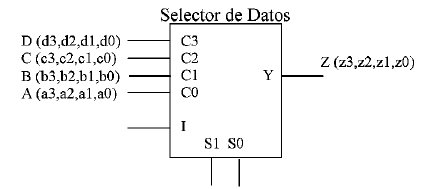

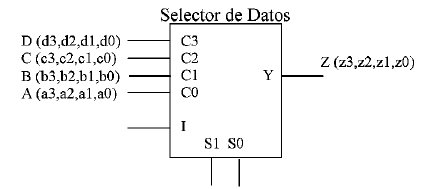

b) Si se desea implementar un circuito selector de datos de 4 bits a partir del multiplexor anterior, determine qué acciones se deberán llevar a cabo:

1 Utilizar 4 Mux 4:1 colocados en paralelo compartiendo los bits de selección, y otro más que reciba como entradas las salidas de los anteriores.

2 Utilizar 4 Mux 4:1 colocados en paralelo compartiendo los bits de selección.

3 Aumentar el número de sus salidas utilizando para ello 8 Mux 4:1.

4 Ninguna de las anteriores.

La acción 2 es la correcta: Utilizar 4 Mux 4:1 colocados en paralelo compartiendo los bits de selección, ya que la salida Z debe tener 4 bits en paralelo y cada multiplexor da como salida uno de los bits. Al compartir las entradas de selección, los 4 multiplexores seleccionan el mismo canal de entrada a la vez. Introduciendo los bits de cada dato por el mismo canal de los multiplexores, estos aparecerán a la vez en la salida.