|

CODIFICADORES |

CODIFICADORES SIN PRIORIDAD

Los codificadores sin prioridad son aquellos que cuando se les aplican dos o más señales de entrada presentan una salida que no corresponde a la codificación de una señal de entrada.

Un ejemplo de codificador sin prioridad se puede realizar con una matriz de diodos como el de la figura.

Al activar el interruptor del número decimal, la salida es su código en binario decimal (código BCD).

Si están activados dos o más interruptores a la vez el código será incorrecto, ya que conducirán todos los diodos activados.

Un codificador de 8 entradas sin prioridad realizado con puertas lógicas tiene la siguiente tabla de verdad:

| Entradas | A2 | A1 | A0 |

|---|---|---|---|

E0 |

0 |

0 |

0 |

E1 |

0 |

0 |

1 |

E2 |

0 |

1 |

0 |

E3 |

0 |

1 |

1 |

E4 |

1 |

0 |

0 |

E5 |

1 |

0 |

1 |

E6 |

1 |

1 |

0 |

E7 |

1 |

1 |

1 |

De la tabla de verdad se deducen las siguientes expresiones lógicas para las salidas:

A2 = E4 + E5 + E6 + E7

A1 = E2 + E3 + E6 + E7

A0 = E1 + E3 + E5 + E7

El circuito lógico es el siguiente:

CODIFICADORES CON PRIORIDAD

Para evitar los errores que se producen en un codificador sin prioridad se encuentran los codificadores prioritarios, es decir, en los que las salidas representan el código binario correspondiente a la entrada activa que tenga mayor valor decimal (prioridad ascendente), en caso de que varias entradas estén activadas simultáneamente. Cuando la entrada que actúa sobre la salida es la menor de todas las entradas activadas, se denomina prioridad descendente.

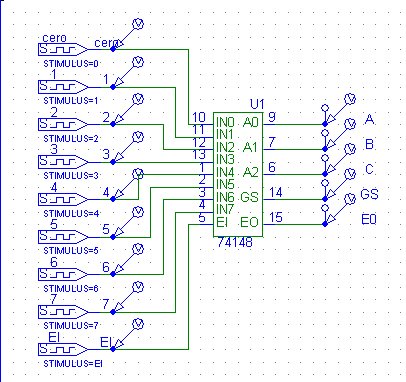

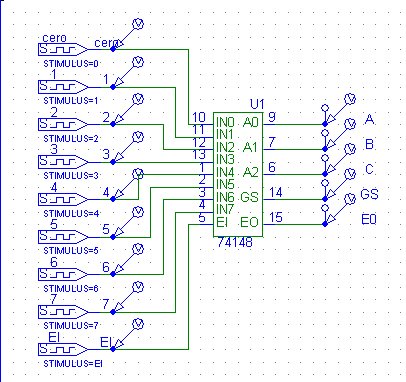

En la siguiente figura tenemos como ejemplo de codificador con prioridad ascendente el circuito integrado TTL 74148, que tiene 8 (23) líneas de entrada (0 a 7), y 3 líneas de salida. La relación de pines de este integrado es la siguiente:

0, 1, 2, 3, 4, 5, 6, 7 : entradas activas a niveles bajos (0V).

EI: entrada de inhibición que debe estar a nivel bajo (0V) para que se realice la codificación.

C, B y A: en las salidas aparecen, activas también a nivel bajo (0V), los datos codificados en binario de tres bits (4-2-1).

E0: que, en nivel bajo, indica que ninguna de las entradas es activa (sirve para distinguir entre las situaciones de activación de la entrada 0 y ninguna entrada activa, ya que en ambos casos las salidas están a nivel alto).

GS: que pasa a nivel bajo cuando alguna de las entradas es activa.

La tabla de verdad y el montaje del codificador es la siguiente:

La simulación con microsim de este componente nos proporciona el siguiente esquemático y cronograma:

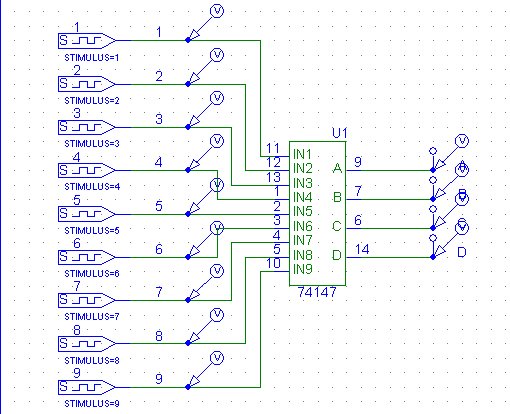

Otro ejemplo de codificador prioritario es el circuito integrado TTL 74147 que tiene 9 entradas que se codifican en un dato de 4 salidas en BCD (8-4-2-1).

La relación de pines de este integrado es la siguiente:

1, 2, 3, 4, 5, 6, 7, 8, 9: entradas activas a niveles bajos (0V).

D, C, B y A: en las salidas aparecen, activas también a nivel bajo (0V), los datos codificados en binario de cuatro bits (8-4-2-1).

La tabla de verdad y el montaje del codificador es la siguiente:

Para representar el cero decimal todas las entradas están en el nivel alto (5V). Para que aparezca el código en binario con LEDs encendidos del número activado a la entrada, colocamos a 5V la otra patilla. Así, cuando aparezcan 0V a la salida (activa) se enciende y con 5V a la salida (inactiva) se apague.

El esquema realizado para la simulación del circuito integrado TTL 74147 en microsim es el siguiente:

La simulación nos da el siguiente cronograma: